Product Summary

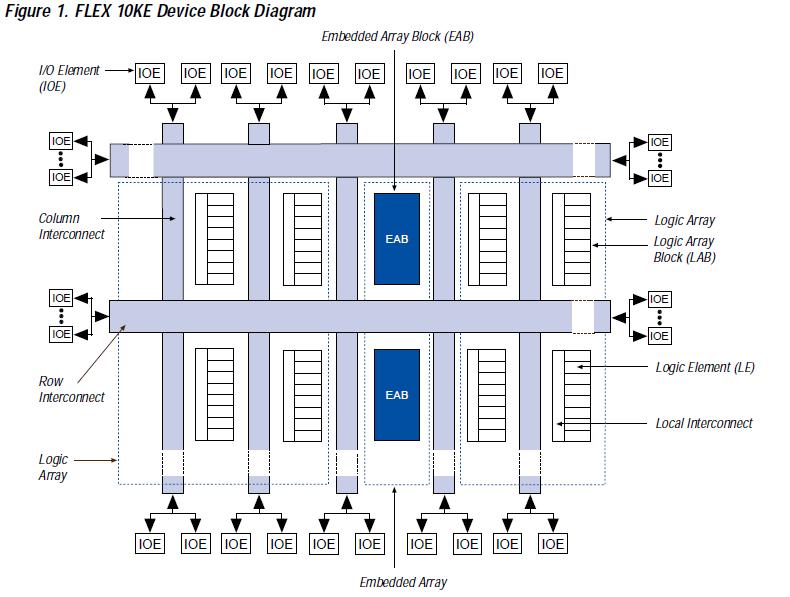

The EPF10K50EQC240-3 is an Embedded Programmable Logic Device. It features necessary to implement common gate array megafunctions. With up to 200,000 typical gates, the EPF10K50EQC240-3 provides the density, speed, and features to integrate entire systems, including multiple 32-bit buses, into a single device. The ability to reconfigure the EPF10K50EQC240-3 enables 100% testing prior to shipment and allows the designer to focus on simulation and design verification. It reconfigurability eliminates inventory management for gate array designs and generation of test vectors for fault coverage.

Parametrics

EPF10K50EQC240-3 absolute maximum ratings: (1)VCCINT, Supply voltage, With respect to ground: –0.5 to 3.6 V; (2)VCCIO, supply voltage, With respect to ground: –0.5 to 4.6 V; (3)VI, DC input voltage: –2.0 to 5.75 V; (4)IOUT, DC output current, per pin: –25 to 25 mA; (5)TSTG, Storage temperature No bias: –65 to 150℃; (6)TAMB, Ambient temperature Under bias: –65 to 135℃; (7)TJ, Junction temperature PQFP, TQFP, BGA, and FineLine BGA; (8)packages, under bias: 135℃; Ceramic PGA packages, under bias: 150℃; (9)VCCINT, Supply voltage for internal logic and input buffers: 2.30 to 2.70V; (10)VCCIO, Supply voltage for output buffers, 3.3-V operation: 3.00 to 3.60V; Supply voltage for output buffers, 2.5-V operation: 2.30 to 2.70V; (11)VI, Input voltage: –0.5 to 5.75V; (12)VO, Output voltage: 0 V to CCIO V; (13)TA, Ambient temperature, For commercial use: 0 to 70℃; For industrial use: –40 to 85℃; (14)TJ, Operating temperature, For commercial use: 0 to 85℃; For industrial use: –40 to 100℃; (15)tR, Input rise time: 40ns; (16)tF, Input fall time: 40ns.

Features

EPF10K50EQC240-3 features: (1)Embedded programmable logic devices (PLDs), providing system-on-a-programmable-chip (SOPC) integration in a single device; (2)Enhanced embedded array for implementing megafunctions such as efficient memory and specialized logic functions; (3)Dual-port capability with up to 16-bit width per embedded array; (4)block (EAB); (5)Logic array for general logic functions; (6)High density: 30,000 to 200,000 typical gates; (7)Up to 98,304 RAM bits (4,096 bits per EAB), all of which can be used without reducing logic capacity; (8)MultiVoltTM I/O pins can drive or be driven by 2.5-V, 3.3-V, or 5.0-V devices; (9)Low power consumption; (10)Bidirectional I/O performance (tSU and tCO) up to 212 MHz; (11)Fully compliant with the PCI Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2 for 3.3-V operation at 33 MHz or 66 MHz; (12)-1 speed grade devices are compliant with PCI Local Bus Specification, Revision 2.2, for 5.0-V operation; (13)Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990, available without consuming additional device logic.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EPF10K50EQC240-3 |

|

IC FLEX 10KE FPGA 50K 240-PQFP |

Data Sheet |

|

|

||||||

|

EPF10K50EQC240-3N |

|

IC FLEX 10KE FPGA 50K 240-PQFP |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))